bq2588x_reg.h File Reference

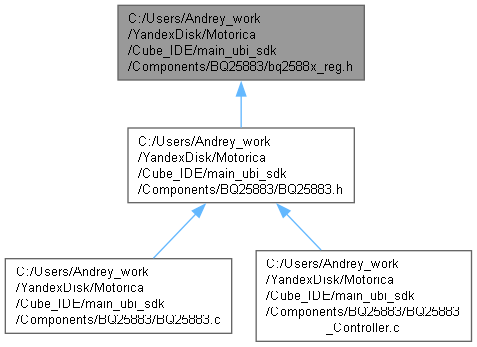

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Macro Definition Documentation

◆ BQ2588X_ADC_DONE_INT_MASK_MASK

| #define BQ2588X_ADC_DONE_INT_MASK_MASK 0x80 |

◆ BQ2588X_ADC_DONE_INT_MASK_SHIFT

| #define BQ2588X_ADC_DONE_INT_MASK_SHIFT 7 |

◆ BQ2588X_ADC_DONE_STAT_MASK

| #define BQ2588X_ADC_DONE_STAT_MASK 0x80 |

◆ BQ2588X_ADC_SCAN_12BITS

| #define BQ2588X_ADC_SCAN_12BITS 3 |

◆ BQ2588X_ADC_SCAN_13BITS

| #define BQ2588X_ADC_SCAN_13BITS 2 |

◆ BQ2588X_ADC_SCAN_14BITS

| #define BQ2588X_ADC_SCAN_14BITS 1 |

◆ BQ2588X_ADC_SCAN_15BITS

| #define BQ2588X_ADC_SCAN_15BITS 0 |

◆ BQ2588X_ADC_SCAN_BITS_MASK

| #define BQ2588X_ADC_SCAN_BITS_MASK 0x30 |

◆ BQ2588X_ADC_SCAN_BITS_SHIFT

| #define BQ2588X_ADC_SCAN_BITS_SHIFT 4 |

◆ BQ2588X_ADC_SCAN_CONTINUOUS

| #define BQ2588X_ADC_SCAN_CONTINUOUS 0 |

◆ BQ2588X_ADC_SCAN_DISABLE

| #define BQ2588X_ADC_SCAN_DISABLE 0 |

◆ BQ2588X_ADC_SCAN_EN_MASK

| #define BQ2588X_ADC_SCAN_EN_MASK 0x80 |

◆ BQ2588X_ADC_SCAN_EN_SHIFT

| #define BQ2588X_ADC_SCAN_EN_SHIFT 7 |

◆ BQ2588X_ADC_SCAN_ENABLE

| #define BQ2588X_ADC_SCAN_ENABLE 1 |

◆ BQ2588X_ADC_SCAN_ONESHOT

| #define BQ2588X_ADC_SCAN_ONESHOT 1 |

◆ BQ2588X_ADC_SCAN_RATE_MASK

| #define BQ2588X_ADC_SCAN_RATE_MASK 0x40 |

◆ BQ2588X_ADC_SCAN_RATE_SHIFT

| #define BQ2588X_ADC_SCAN_RATE_SHIFT 6 |

◆ BQ2588X_AUTO_DPDM_DISABLE

| #define BQ2588X_AUTO_DPDM_DISABLE 0 |

◆ BQ2588X_AUTO_DPDM_ENABLE

| #define BQ2588X_AUTO_DPDM_ENABLE 1 |

◆ BQ2588X_AUTO_DPDM_MASK

| #define BQ2588X_AUTO_DPDM_MASK 0x40 |

◆ BQ2588X_AUTO_DPDM_SHIFT

| #define BQ2588X_AUTO_DPDM_SHIFT 6 |

◆ BQ2588X_BAT_DISCHG_LOAD_DISABLE

| #define BQ2588X_BAT_DISCHG_LOAD_DISABLE 0 |

◆ BQ2588X_BAT_DISCHG_LOAD_ENABLE

| #define BQ2588X_BAT_DISCHG_LOAD_ENABLE 1 |

◆ BQ2588X_BAT_DISCHG_LOAD_MASK

| #define BQ2588X_BAT_DISCHG_LOAD_MASK 0x40 |

◆ BQ2588X_BAT_DISCHG_LOAD_SHIFT

| #define BQ2588X_BAT_DISCHG_LOAD_SHIFT 6 |

◆ BQ2588X_BAT_OVP_FLAG_ACTIVE

| #define BQ2588X_BAT_OVP_FLAG_ACTIVE 1 |

◆ BQ2588X_BAT_OVP_FLAG_INACTIVE

| #define BQ2588X_BAT_OVP_FLAG_INACTIVE 0 |

◆ BQ2588X_BAT_OVP_FLAG_MASK

| #define BQ2588X_BAT_OVP_FLAG_MASK 0x20 |

◆ BQ2588X_BAT_OVP_FLAG_SHIFT

| #define BQ2588X_BAT_OVP_FLAG_SHIFT 5 |

◆ BQ2588X_BAT_OVP_INT_MASK_DISABLE

| #define BQ2588X_BAT_OVP_INT_MASK_DISABLE 0 |

◆ BQ2588X_BAT_OVP_INT_MASK_ENABLE

| #define BQ2588X_BAT_OVP_INT_MASK_ENABLE 1 |

◆ BQ2588X_BAT_OVP_INT_MASK_MASK

| #define BQ2588X_BAT_OVP_INT_MASK_MASK 0x20 |

◆ BQ2588X_BAT_OVP_INT_MASK_SHIFT

| #define BQ2588X_BAT_OVP_INT_MASK_SHIFT 5 |

◆ BQ2588X_BAT_OVP_STAT_ACTIVE

| #define BQ2588X_BAT_OVP_STAT_ACTIVE 1 |

◆ BQ2588X_BAT_OVP_STAT_INACTIVE

| #define BQ2588X_BAT_OVP_STAT_INACTIVE 0 |

◆ BQ2588X_BAT_OVP_STAT_MASK

| #define BQ2588X_BAT_OVP_STAT_MASK 0x20 |

◆ BQ2588X_BAT_OVP_STAT_SHIFT

| #define BQ2588X_BAT_OVP_STAT_SHIFT 5 |

◆ BQ2588X_BATLOW_VOLT_5P6V

| #define BQ2588X_BATLOW_VOLT_5P6V 0 |

◆ BQ2588X_BATLOW_VOLT_6V

| #define BQ2588X_BATLOW_VOLT_6V 1 |

◆ BQ2588X_BATLOW_VOLT_MASK

| #define BQ2588X_BATLOW_VOLT_MASK 0x04 |

◆ BQ2588X_BATLOW_VOLT_SHIFT

| #define BQ2588X_BATLOW_VOLT_SHIFT 2 |

◆ BQ2588X_CHARGE_DISABLE

| #define BQ2588X_CHARGE_DISABLE 0 |

◆ BQ2588X_CHARGE_EN_MASK

| #define BQ2588X_CHARGE_EN_MASK 0x08 |

◆ BQ2588X_CHARGE_EN_SHIFT

| #define BQ2588X_CHARGE_EN_SHIFT 3 |

◆ BQ2588X_CHARGE_ENABLE

| #define BQ2588X_CHARGE_ENABLE 1 |

◆ BQ2588X_CHRG_FLAG_CHANGED

| #define BQ2588X_CHRG_FLAG_CHANGED 1 |

◆ BQ2588X_CHRG_FLAG_MASK

| #define BQ2588X_CHRG_FLAG_MASK 0x01 |

◆ BQ2588X_CHRG_FLAG_NORMAL

| #define BQ2588X_CHRG_FLAG_NORMAL 0 |

◆ BQ2588X_CHRG_FLAG_SHIFT

| #define BQ2588X_CHRG_FLAG_SHIFT 0 |

◆ BQ2588X_CHRG_INT_MASK_DISABLE

| #define BQ2588X_CHRG_INT_MASK_DISABLE 0 |

◆ BQ2588X_CHRG_INT_MASK_ENABLE

| #define BQ2588X_CHRG_INT_MASK_ENABLE 1 |

◆ BQ2588X_CHRG_INT_MASK_MASK

| #define BQ2588X_CHRG_INT_MASK_MASK 0x01 |

◆ BQ2588X_CHRG_INT_MASK_SHIFT

| #define BQ2588X_CHRG_INT_MASK_SHIFT 0 |

◆ BQ2588X_CHRG_STAT_DONE

| #define BQ2588X_CHRG_STAT_DONE 6 |

◆ BQ2588X_CHRG_STAT_FAST

| #define BQ2588X_CHRG_STAT_FAST 3 |

◆ BQ2588X_CHRG_STAT_IDLE

| #define BQ2588X_CHRG_STAT_IDLE 0 |

◆ BQ2588X_CHRG_STAT_MASK

| #define BQ2588X_CHRG_STAT_MASK 0x07 |

◆ BQ2588X_CHRG_STAT_PRECHG

| #define BQ2588X_CHRG_STAT_PRECHG 2 |

◆ BQ2588X_CHRG_STAT_RSVED

| #define BQ2588X_CHRG_STAT_RSVED 7 |

◆ BQ2588X_CHRG_STAT_SHIFT

| #define BQ2588X_CHRG_STAT_SHIFT 0 |

◆ BQ2588X_CHRG_STAT_TAPER

| #define BQ2588X_CHRG_STAT_TAPER 4 |

◆ BQ2588X_CHRG_STAT_TOPOFF

| #define BQ2588X_CHRG_STAT_TOPOFF 5 |

◆ BQ2588X_CHRG_STAT_TRICKLE

| #define BQ2588X_CHRG_STAT_TRICKLE 1 |

◆ BQ2588X_DO_FORCE

| #define BQ2588X_DO_FORCE 1 |

◆ BQ2588X_DO_NOT_FORCE

| #define BQ2588X_DO_NOT_FORCE 0 |

◆ BQ2588X_DPDM_DETECT_DISABLE

| #define BQ2588X_DPDM_DETECT_DISABLE 0 |

◆ BQ2588X_DPDM_DETECT_ENABLE

| #define BQ2588X_DPDM_DETECT_ENABLE 1 |

◆ BQ2588X_DPDM_DETECT_MASK

| #define BQ2588X_DPDM_DETECT_MASK 0x40 |

◆ BQ2588X_DPDM_DETECT_SHIFT

| #define BQ2588X_DPDM_DETECT_SHIFT 6 |

◆ BQ2588X_EN_HIZ_MASK

| #define BQ2588X_EN_HIZ_MASK 0x80 |

◆ BQ2588X_EN_HIZ_SHIFT

| #define BQ2588X_EN_HIZ_SHIFT 7 |

◆ BQ2588X_EN_ICO_MASK

| #define BQ2588X_EN_ICO_MASK 0x20 |

◆ BQ2588X_EN_ICO_SHIFT

| #define BQ2588X_EN_ICO_SHIFT 5 |

◆ BQ2588X_EN_ILIM_MASK

| #define BQ2588X_EN_ILIM_MASK 0x40 |

◆ BQ2588X_EN_ILIM_SHIFT

| #define BQ2588X_EN_ILIM_SHIFT 6 |

◆ BQ2588X_FORCE_ICO_MASK

| #define BQ2588X_FORCE_ICO_MASK 0x80 |

◆ BQ2588X_FORCE_ICO_SHIFT

| #define BQ2588X_FORCE_ICO_SHIFT 7 |

◆ BQ2588X_HIZ_DISABLE

| #define BQ2588X_HIZ_DISABLE 0 |

◆ BQ2588X_HIZ_ENABLE

| #define BQ2588X_HIZ_ENABLE 1 |

◆ BQ2588X_IBUS_ADC_DIS_MASK

| #define BQ2588X_IBUS_ADC_DIS_MASK 0x80 |

◆ BQ2588X_IBUS_ADC_DIS_SHIFT

| #define BQ2588X_IBUS_ADC_DIS_SHIFT 7 |

◆ BQ2588X_IBUS_ADC_DISABLE

| #define BQ2588X_IBUS_ADC_DISABLE 1 |

◆ BQ2588X_IBUS_ADC_ENABLE

| #define BQ2588X_IBUS_ADC_ENABLE 0 |

◆ BQ2588X_IBUS_ADC_HB_BASE

| #define BQ2588X_IBUS_ADC_HB_BASE 0 |

◆ BQ2588X_IBUS_ADC_HB_LSB

| #define BQ2588X_IBUS_ADC_HB_LSB 256 |

◆ BQ2588X_IBUS_ADC_HB_MASK

| #define BQ2588X_IBUS_ADC_HB_MASK 0xFF |

◆ BQ2588X_IBUS_ADC_HB_SHIFT

| #define BQ2588X_IBUS_ADC_HB_SHIFT 0 |

◆ BQ2588X_IBUS_ADC_LB_BASE

| #define BQ2588X_IBUS_ADC_LB_BASE 0 |

◆ BQ2588X_IBUS_ADC_LB_LSB

| #define BQ2588X_IBUS_ADC_LB_LSB 1 |

◆ BQ2588X_IBUS_ADC_LB_MASK

| #define BQ2588X_IBUS_ADC_LB_MASK 0xFF |

◆ BQ2588X_IBUS_ADC_LB_SHIFT

| #define BQ2588X_IBUS_ADC_LB_SHIFT 0 |

◆ BQ2588X_ICHG_ADC_DIS_MASK

| #define BQ2588X_ICHG_ADC_DIS_MASK 0x40 |

◆ BQ2588X_ICHG_ADC_DIS_SHIFT

| #define BQ2588X_ICHG_ADC_DIS_SHIFT 6 |

◆ BQ2588X_ICHG_ADC_DISABLE

| #define BQ2588X_ICHG_ADC_DISABLE 1 |

◆ BQ2588X_ICHG_ADC_ENABLE

| #define BQ2588X_ICHG_ADC_ENABLE 0 |

◆ BQ2588X_ICHG_ADC_HB_BASE

| #define BQ2588X_ICHG_ADC_HB_BASE 0 |

◆ BQ2588X_ICHG_ADC_HB_LSB

| #define BQ2588X_ICHG_ADC_HB_LSB 256 |

◆ BQ2588X_ICHG_ADC_HB_MASK

| #define BQ2588X_ICHG_ADC_HB_MASK 0xFF |

◆ BQ2588X_ICHG_ADC_HB_SHIFT

| #define BQ2588X_ICHG_ADC_HB_SHIFT 0 |

◆ BQ2588X_ICHG_ADC_LB_BASE

| #define BQ2588X_ICHG_ADC_LB_BASE 0 |

◆ BQ2588X_ICHG_ADC_LB_LSB

| #define BQ2588X_ICHG_ADC_LB_LSB 1 |

◆ BQ2588X_ICHG_ADC_LB_MASK

| #define BQ2588X_ICHG_ADC_LB_MASK 0xFF |

◆ BQ2588X_ICHG_ADC_LB_SHIFT

| #define BQ2588X_ICHG_ADC_LB_SHIFT 0 |

◆ BQ2588X_ICHG_BASE

| #define BQ2588X_ICHG_BASE 0 |

◆ BQ2588X_ICHG_LSB

| #define BQ2588X_ICHG_LSB 50 |

◆ BQ2588X_ICHG_MASK

| #define BQ2588X_ICHG_MASK 0x3F |

◆ BQ2588X_ICHG_SHIFT

| #define BQ2588X_ICHG_SHIFT 0 |

◆ BQ2588X_ICO_DISABLE

| #define BQ2588X_ICO_DISABLE 0 |

◆ BQ2588X_ICO_DISABLED

| #define BQ2588X_ICO_DISABLED 0 |

◆ BQ2588X_ICO_DONE

| #define BQ2588X_ICO_DONE 2 |

◆ BQ2588X_ICO_ENABLE

| #define BQ2588X_ICO_ENABLE 1 |

◆ BQ2588X_ICO_FLAG_CHANGED

| #define BQ2588X_ICO_FLAG_CHANGED 1 |

◆ BQ2588X_ICO_FLAG_MASK

| #define BQ2588X_ICO_FLAG_MASK 0x02 |

◆ BQ2588X_ICO_FLAG_NORMAL

| #define BQ2588X_ICO_FLAG_NORMAL 0 |

◆ BQ2588X_ICO_FLAG_SHIFT

| #define BQ2588X_ICO_FLAG_SHIFT 1 |

◆ BQ2588X_ICO_ILIM_BASE

| #define BQ2588X_ICO_ILIM_BASE 500 |

◆ BQ2588X_ICO_ILIM_LSB

| #define BQ2588X_ICO_ILIM_LSB 100 |

◆ BQ2588X_ICO_ILIM_MASK

| #define BQ2588X_ICO_ILIM_MASK 0x1F |

◆ BQ2588X_ICO_ILIM_SHIFT

| #define BQ2588X_ICO_ILIM_SHIFT 0 |

◆ BQ2588X_ICO_IN_PROGRESS

| #define BQ2588X_ICO_IN_PROGRESS 1 |

◆ BQ2588X_ICO_INT_MASK_DISABLE

| #define BQ2588X_ICO_INT_MASK_DISABLE 0 |

◆ BQ2588X_ICO_INT_MASK_ENABLE

| #define BQ2588X_ICO_INT_MASK_ENABLE 1 |

◆ BQ2588X_ICO_INT_MASK_MASK

| #define BQ2588X_ICO_INT_MASK_MASK 0x02 |

◆ BQ2588X_ICO_INT_MASK_SHIFT

| #define BQ2588X_ICO_INT_MASK_SHIFT 1 |

◆ BQ2588X_ICO_STAT_MASK

| #define BQ2588X_ICO_STAT_MASK 0x06 |

◆ BQ2588X_ICO_STAT_SHIFT

| #define BQ2588X_ICO_STAT_SHIFT 1 |

◆ BQ2588X_IINDPM_FLAG_ACTIVE

| #define BQ2588X_IINDPM_FLAG_ACTIVE 1 |

◆ BQ2588X_IINDPM_FLAG_INACTIVE

| #define BQ2588X_IINDPM_FLAG_INACTIVE 0 |

◆ BQ2588X_IINDPM_FLAG_MASK

| #define BQ2588X_IINDPM_FLAG_MASK 0x40 |

◆ BQ2588X_IINDPM_FLAG_SHIFT

| #define BQ2588X_IINDPM_FLAG_SHIFT 6 |

◆ BQ2588X_IINDPM_INT_MASK_DISABLE

| #define BQ2588X_IINDPM_INT_MASK_DISABLE 0 |

◆ BQ2588X_IINDPM_INT_MASK_ENABLE

| #define BQ2588X_IINDPM_INT_MASK_ENABLE 1 |

◆ BQ2588X_IINDPM_INT_MASK_MASK

| #define BQ2588X_IINDPM_INT_MASK_MASK 0x40 |

◆ BQ2588X_IINDPM_INT_MASK_SHIFT

| #define BQ2588X_IINDPM_INT_MASK_SHIFT 6 |

◆ BQ2588X_IINDPM_STAT_ACTIVE

| #define BQ2588X_IINDPM_STAT_ACTIVE 1 |

◆ BQ2588X_IINDPM_STAT_INACTIVE

| #define BQ2588X_IINDPM_STAT_INACTIVE 0 |

◆ BQ2588X_IINDPM_STAT_MASK

| #define BQ2588X_IINDPM_STAT_MASK 0x40 |

◆ BQ2588X_IINDPM_STAT_SHIFT

| #define BQ2588X_IINDPM_STAT_SHIFT 6 |

◆ BQ2588X_IINDPM_TH_BASE

| #define BQ2588X_IINDPM_TH_BASE 500 |

◆ BQ2588X_IINDPM_TH_LSB

| #define BQ2588X_IINDPM_TH_LSB 100 |

◆ BQ2588X_IINDPM_TH_MASK

| #define BQ2588X_IINDPM_TH_MASK 0x1F |

◆ BQ2588X_IINDPM_TH_SHIFT

| #define BQ2588X_IINDPM_TH_SHIFT 0 |

◆ BQ2588X_ILIM_PIN_DISABLE

| #define BQ2588X_ILIM_PIN_DISABLE 0 |

◆ BQ2588X_ILIM_PIN_ENABLE

| #define BQ2588X_ILIM_PIN_ENABLE 1 |

◆ BQ2588X_IPRECHG_BASE

| #define BQ2588X_IPRECHG_BASE 50 |

◆ BQ2588X_IPRECHG_LSB

| #define BQ2588X_IPRECHG_LSB 50 |

◆ BQ2588X_IPRECHG_MASK

| #define BQ2588X_IPRECHG_MASK 0xF0 |

◆ BQ2588X_IPRECHG_SHIFT

| #define BQ2588X_IPRECHG_SHIFT 4 |

◆ BQ2588X_ITERM_BASE

| #define BQ2588X_ITERM_BASE 50 |

◆ BQ2588X_ITERM_LSB

| #define BQ2588X_ITERM_LSB 50 |

◆ BQ2588X_ITERM_MASK

| #define BQ2588X_ITERM_MASK 0x0F |

◆ BQ2588X_ITERM_SHIFT

| #define BQ2588X_ITERM_SHIFT 0 |

◆ BQ2588X_OTG_DISABLE

| #define BQ2588X_OTG_DISABLE 0 |

◆ BQ2588X_OTG_EN_MASK

| #define BQ2588X_OTG_EN_MASK 0x80 |

◆ BQ2588X_OTG_EN_SHIFT

| #define BQ2588X_OTG_EN_SHIFT 7 |

◆ BQ2588X_OTG_ENABLE

| #define BQ2588X_OTG_ENABLE 1 |

◆ BQ2588X_OTG_FLAG_BUS_OVERLOAD

| #define BQ2588X_OTG_FLAG_BUS_OVERLOAD 1 |

◆ BQ2588X_OTG_FLAG_MASK

| #define BQ2588X_OTG_FLAG_MASK 0x01 |

◆ BQ2588X_OTG_FLAG_NORMAL

| #define BQ2588X_OTG_FLAG_NORMAL 0 |

◆ BQ2588X_OTG_FLAG_SHIFT

| #define BQ2588X_OTG_FLAG_SHIFT 0 |

◆ BQ2588X_OTG_ILIM_BASE

| #define BQ2588X_OTG_ILIM_BASE 500 |

◆ BQ2588X_OTG_ILIM_LSB

| #define BQ2588X_OTG_ILIM_LSB 100 |

◆ BQ2588X_OTG_ILIM_MASK

| #define BQ2588X_OTG_ILIM_MASK 0xF0 |

◆ BQ2588X_OTG_ILIM_SHIFT

| #define BQ2588X_OTG_ILIM_SHIFT 4 |

◆ BQ2588X_OTG_INT_MASK_DISABLE

| #define BQ2588X_OTG_INT_MASK_DISABLE 0 |

◆ BQ2588X_OTG_INT_MASK_ENABLE

| #define BQ2588X_OTG_INT_MASK_ENABLE 1 |

◆ BQ2588X_OTG_INT_MASK_MASK

| #define BQ2588X_OTG_INT_MASK_MASK 0x01 |

◆ BQ2588X_OTG_INT_MASK_SHIFT

| #define BQ2588X_OTG_INT_MASK_SHIFT 0 |

◆ BQ2588X_OTG_STAT_BUS_OVERLOAD

| #define BQ2588X_OTG_STAT_BUS_OVERLOAD 1 |

◆ BQ2588X_OTG_STAT_MASK

| #define BQ2588X_OTG_STAT_MASK 0x01 |

◆ BQ2588X_OTG_STAT_NORMAL

| #define BQ2588X_OTG_STAT_NORMAL 0 |

◆ BQ2588X_OTG_STAT_SHIFT

| #define BQ2588X_OTG_STAT_SHIFT 0 |

◆ BQ2588X_OTG_VLIM_BASE

| #define BQ2588X_OTG_VLIM_BASE 4500 |

◆ BQ2588X_OTG_VLIM_LSB

| #define BQ2588X_OTG_VLIM_LSB 100 |

◆ BQ2588X_OTG_VLIM_MASK

| #define BQ2588X_OTG_VLIM_MASK 0x0F |

◆ BQ2588X_OTG_VLIM_SHIFT

| #define BQ2588X_OTG_VLIM_SHIFT 0 |

◆ BQ2588X_PART_NO_BQ25880

| #define BQ2588X_PART_NO_BQ25880 1 |

◆ BQ2588X_PART_NO_BQ25881_3

| #define BQ2588X_PART_NO_BQ25881_3 3 |

◆ BQ2588X_PART_NO_BQ25882

| #define BQ2588X_PART_NO_BQ25882 2 |

◆ BQ2588X_PART_NO_MASK

| #define BQ2588X_PART_NO_MASK 0x38 |

◆ BQ2588X_PART_NO_SHIFT

| #define BQ2588X_PART_NO_SHIFT 3 |

◆ BQ2588X_PG_FLAG_GOOD

| #define BQ2588X_PG_FLAG_GOOD 1 |

◆ BQ2588X_PG_FLAG_MASK

| #define BQ2588X_PG_FLAG_MASK 0x80 |

◆ BQ2588X_PG_FLAG_POOR

| #define BQ2588X_PG_FLAG_POOR 0 |

◆ BQ2588X_PG_FLAG_SHIFT

| #define BQ2588X_PG_FLAG_SHIFT 7 |

◆ BQ2588X_PG_INT_MASK_DISABLE

| #define BQ2588X_PG_INT_MASK_DISABLE 0 |

◆ BQ2588X_PG_INT_MASK_ENABLE

| #define BQ2588X_PG_INT_MASK_ENABLE 1 |

◆ BQ2588X_PG_INT_MASK_MASK

| #define BQ2588X_PG_INT_MASK_MASK 0x80 |

◆ BQ2588X_PG_INT_MASK_SHIFT

| #define BQ2588X_PG_INT_MASK_SHIFT 7 |

◆ BQ2588X_PG_STAT_GOOD

| #define BQ2588X_PG_STAT_GOOD 1 |

◆ BQ2588X_PG_STAT_MASK

| #define BQ2588X_PG_STAT_MASK 0x80 |

◆ BQ2588X_PG_STAT_POOR

| #define BQ2588X_PG_STAT_POOR 0 |

◆ BQ2588X_PG_STAT_SHIFT

| #define BQ2588X_PG_STAT_SHIFT 7 |

◆ BQ2588X_RECHG_VOLT_BASE

| #define BQ2588X_RECHG_VOLT_BASE 100 |

◆ BQ2588X_RECHG_VOLT_LSB

| #define BQ2588X_RECHG_VOLT_LSB 100 |

◆ BQ2588X_RECHG_VOLT_MASK

| #define BQ2588X_RECHG_VOLT_MASK 0x03 |

◆ BQ2588X_RECHG_VOLT_SHIFT

| #define BQ2588X_RECHG_VOLT_SHIFT 0 |

◆ BQ2588X_REG_ADC_CTRL

| #define BQ2588X_REG_ADC_CTRL 0x15 |

◆ BQ2588X_REG_ADC_FUNC_DIS

| #define BQ2588X_REG_ADC_FUNC_DIS 0x16 |

◆ BQ2588X_REG_CHARGE_CURRENT

| #define BQ2588X_REG_CHARGE_CURRENT 0x01 |

◆ BQ2588X_REG_CHARGE_VOLT

| #define BQ2588X_REG_CHARGE_VOLT 0x00 |

◆ BQ2588X_REG_CHG_CTRL1

| #define BQ2588X_REG_CHG_CTRL1 0x05 |

◆ BQ2588X_REG_CHG_CTRL2

| #define BQ2588X_REG_CHG_CTRL2 0x06 |

◆ BQ2588X_REG_CHG_CTRL3

| #define BQ2588X_REG_CHG_CTRL3 0x07 |

◆ BQ2588X_REG_CHG_FLAG1

| #define BQ2588X_REG_CHG_FLAG1 0x0F |

◆ BQ2588X_REG_CHG_FLAG2

| #define BQ2588X_REG_CHG_FLAG2 0x10 |

◆ BQ2588X_REG_CHG_INT_MASK1

| #define BQ2588X_REG_CHG_INT_MASK1 0x12 |

◆ BQ2588X_REG_CHG_INT_MASK2

| #define BQ2588X_REG_CHG_INT_MASK2 0x13 |

◆ BQ2588X_REG_CHG_STATUS1

| #define BQ2588X_REG_CHG_STATUS1 0x0B |

◆ BQ2588X_REG_CHG_STATUS2

| #define BQ2588X_REG_CHG_STATUS2 0x0c |

◆ BQ2588X_REG_FAULT_FLAG

| #define BQ2588X_REG_FAULT_FLAG 0x11 |

◆ BQ2588X_REG_FAULT_INT_MASK

| #define BQ2588X_REG_FAULT_INT_MASK 0x14 |

◆ BQ2588X_REG_FAULT_STATUS

| #define BQ2588X_REG_FAULT_STATUS 0x0E |

◆ BQ2588X_REG_IBUS_ADC_0

| #define BQ2588X_REG_IBUS_ADC_0 0x18 |

◆ BQ2588X_REG_IBUS_ADC_1

| #define BQ2588X_REG_IBUS_ADC_1 0x17 |

◆ BQ2588X_REG_ICHG_ADC_0

| #define BQ2588X_REG_ICHG_ADC_0 0x1A |

◆ BQ2588X_REG_ICHG_ADC_1

| #define BQ2588X_REG_ICHG_ADC_1 0x19 |

◆ BQ2588X_REG_ICO_LIMIT

| #define BQ2588X_REG_ICO_LIMIT 0x0A |

◆ BQ2588X_REG_IINDPM

| #define BQ2588X_REG_IINDPM 0x03 |

◆ BQ2588X_REG_NTC_STATUS

| #define BQ2588X_REG_NTC_STATUS 0x0D |

◆ BQ2588X_REG_OTG_CTRL

| #define BQ2588X_REG_OTG_CTRL 0x09 |

◆ BQ2588X_REG_PART_NUM

| #define BQ2588X_REG_PART_NUM 0x25 |

◆ BQ2588X_REG_PRECHG_TERM

| #define BQ2588X_REG_PRECHG_TERM 0x04 |

◆ BQ2588X_REG_RESET_IDLE

| #define BQ2588X_REG_RESET_IDLE 0 |

◆ BQ2588X_REG_RESET_KICK

| #define BQ2588X_REG_RESET_KICK 1 |

◆ BQ2588X_REG_RESET_MASK

| #define BQ2588X_REG_RESET_MASK 0x80 |

◆ BQ2588X_REG_RESET_SHIFT

| #define BQ2588X_REG_RESET_SHIFT 7 |

◆ BQ2588X_REG_TDIE_ADC_0

| #define BQ2588X_REG_TDIE_ADC_0 0x24 |

◆ BQ2588X_REG_TDIE_ADC_1

| #define BQ2588X_REG_TDIE_ADC_1 0x23 |

◆ BQ2588X_REG_TS_ADC_0

| #define BQ2588X_REG_TS_ADC_0 0x22 |

◆ BQ2588X_REG_TS_ADC_1

| #define BQ2588X_REG_TS_ADC_1 0x21 |

◆ BQ2588X_REG_VBAT_ADC_0

| #define BQ2588X_REG_VBAT_ADC_0 0x1E |

◆ BQ2588X_REG_VBAT_ADC_1

| #define BQ2588X_REG_VBAT_ADC_1 0x1D |

◆ BQ2588X_REG_VBUS_ADC_0

| #define BQ2588X_REG_VBUS_ADC_0 0x1C |

◆ BQ2588X_REG_VBUS_ADC_1

| #define BQ2588X_REG_VBUS_ADC_1 0x1B |

◆ BQ2588X_REG_VINDPM

| #define BQ2588X_REG_VINDPM 0x02 |

◆ BQ2588X_REG_VSYS_ADC_0

| #define BQ2588X_REG_VSYS_ADC_0 0x20 |

◆ BQ2588X_REG_VSYS_ADC_1

| #define BQ2588X_REG_VSYS_ADC_1 0x1F |

◆ BQ2588X_RESERVED

| #define BQ2588X_RESERVED 3 |

◆ BQ2588X_REV_1P0

| #define BQ2588X_REV_1P0 0 |

◆ BQ2588X_REV_1P1

| #define BQ2588X_REV_1P1 1 |

◆ BQ2588X_REVISION_MASK

| #define BQ2588X_REVISION_MASK 0x07 |

◆ BQ2588X_REVISION_SHIFT

| #define BQ2588X_REVISION_SHIFT 0 |

◆ BQ2588X_SAFETY_TIMER_12H

| #define BQ2588X_SAFETY_TIMER_12H 2 |

◆ BQ2588X_SAFETY_TIMER_20H

| #define BQ2588X_SAFETY_TIMER_20H 3 |

◆ BQ2588X_SAFETY_TIMER_5H

| #define BQ2588X_SAFETY_TIMER_5H 0 |

◆ BQ2588X_SAFETY_TIMER_8H

| #define BQ2588X_SAFETY_TIMER_8H 1 |

◆ BQ2588X_SAFETY_TIMER_DISABLE

| #define BQ2588X_SAFETY_TIMER_DISABLE 0 |

◆ BQ2588X_SAFETY_TIMER_EN_MASK

| #define BQ2588X_SAFETY_TIMER_EN_MASK 0x08 |

◆ BQ2588X_SAFETY_TIMER_EN_SHIFT

| #define BQ2588X_SAFETY_TIMER_EN_SHIFT 3 |

◆ BQ2588X_SAFETY_TIMER_ENABLE

| #define BQ2588X_SAFETY_TIMER_ENABLE 1 |

◆ BQ2588X_SAFETY_TIMER_FLAG_EXPIRED

| #define BQ2588X_SAFETY_TIMER_FLAG_EXPIRED 1 |

◆ BQ2588X_SAFETY_TIMER_FLAG_MASK

| #define BQ2588X_SAFETY_TIMER_FLAG_MASK 0x10 |

◆ BQ2588X_SAFETY_TIMER_FLAG_NORMAL

| #define BQ2588X_SAFETY_TIMER_FLAG_NORMAL 0 |

◆ BQ2588X_SAFETY_TIMER_FLAG_SHIFT

| #define BQ2588X_SAFETY_TIMER_FLAG_SHIFT 4 |

◆ BQ2588X_SAFETY_TIMER_INT_MASK_DISABLE

| #define BQ2588X_SAFETY_TIMER_INT_MASK_DISABLE 0 |

◆ BQ2588X_SAFETY_TIMER_INT_MASK_ENABLE

| #define BQ2588X_SAFETY_TIMER_INT_MASK_ENABLE 1 |

◆ BQ2588X_SAFETY_TIMER_INT_MASK_MASK

| #define BQ2588X_SAFETY_TIMER_INT_MASK_MASK 0x10 |

◆ BQ2588X_SAFETY_TIMER_INT_MASK_SHIFT

| #define BQ2588X_SAFETY_TIMER_INT_MASK_SHIFT 4 |

◆ BQ2588X_SAFETY_TIMER_MASK

| #define BQ2588X_SAFETY_TIMER_MASK 0x06 |

◆ BQ2588X_SAFETY_TIMER_SHIFT

| #define BQ2588X_SAFETY_TIMER_SHIFT 1 |

◆ BQ2588X_SAFETY_TIMER_STAT_EXPIRED

| #define BQ2588X_SAFETY_TIMER_STAT_EXPIRED 1 |

◆ BQ2588X_SAFETY_TIMER_STAT_MASK

| #define BQ2588X_SAFETY_TIMER_STAT_MASK 0x10 |

◆ BQ2588X_SAFETY_TIMER_STAT_NORMAL

| #define BQ2588X_SAFETY_TIMER_STAT_NORMAL 0 |

◆ BQ2588X_SAFETY_TIMER_STAT_SHIFT

| #define BQ2588X_SAFETY_TIMER_STAT_SHIFT 4 |

◆ BQ2588X_SYS_MIN_VOLT_BASE

| #define BQ2588X_SYS_MIN_VOLT_BASE 6000 |

◆ BQ2588X_SYS_MIN_VOLT_LSB

| #define BQ2588X_SYS_MIN_VOLT_LSB 100 |

◆ BQ2588X_SYS_MIN_VOLT_MASK

| #define BQ2588X_SYS_MIN_VOLT_MASK 0x0F |

◆ BQ2588X_SYS_MIN_VOLT_SHIFT

| #define BQ2588X_SYS_MIN_VOLT_SHIFT 0 |

◆ BQ2588X_SYS_SHORT_FLAG_ACTIVE

| #define BQ2588X_SYS_SHORT_FLAG_ACTIVE 1 |

◆ BQ2588X_SYS_SHORT_FLAG_INACTIVE

| #define BQ2588X_SYS_SHORT_FLAG_INACTIVE 0 |

◆ BQ2588X_SYS_SHORT_FLAG_MASK

| #define BQ2588X_SYS_SHORT_FLAG_MASK 0x08 |

◆ BQ2588X_SYS_SHORT_FLAG_SHIFT

| #define BQ2588X_SYS_SHORT_FLAG_SHIFT 3 |

◆ BQ2588X_SYS_SHORT_INT_MASK_DISABLE

| #define BQ2588X_SYS_SHORT_INT_MASK_DISABLE 0 |

◆ BQ2588X_SYS_SHORT_INT_MASK_ENABLE

| #define BQ2588X_SYS_SHORT_INT_MASK_ENABLE 1 |

◆ BQ2588X_SYS_SHORT_INT_MASK_MASK

| #define BQ2588X_SYS_SHORT_INT_MASK_MASK 0x08 |

◆ BQ2588X_SYS_SHORT_INT_MASK_SHIFT

| #define BQ2588X_SYS_SHORT_INT_MASK_SHIFT 3 |

◆ BQ2588X_SYS_SHORT_STAT_ACTIVE

| #define BQ2588X_SYS_SHORT_STAT_ACTIVE 1 |

◆ BQ2588X_SYS_SHORT_STAT_INACTIVE

| #define BQ2588X_SYS_SHORT_STAT_INACTIVE 0 |

◆ BQ2588X_SYS_SHORT_STAT_MASK

| #define BQ2588X_SYS_SHORT_STAT_MASK 0x08 |

◆ BQ2588X_SYS_SHORT_STAT_SHIFT

| #define BQ2588X_SYS_SHORT_STAT_SHIFT 3 |

◆ BQ2588X_TDIE_ADC_DIS_MASK

| #define BQ2588X_TDIE_ADC_DIS_MASK 0x01 |

◆ BQ2588X_TDIE_ADC_DIS_SHIFT

| #define BQ2588X_TDIE_ADC_DIS_SHIFT 0 |

◆ BQ2588X_TDIE_ADC_DISABLE

| #define BQ2588X_TDIE_ADC_DISABLE 1 |

◆ BQ2588X_TDIE_ADC_ENABLE

| #define BQ2588X_TDIE_ADC_ENABLE 0 |

◆ BQ2588X_TDIE_ADC_HB_BASE

| #define BQ2588X_TDIE_ADC_HB_BASE 0 |

◆ BQ2588X_TDIE_ADC_HB_LSB

| #define BQ2588X_TDIE_ADC_HB_LSB 128 |

◆ BQ2588X_TDIE_ADC_HB_MASK

| #define BQ2588X_TDIE_ADC_HB_MASK 0xFF |

◆ BQ2588X_TDIE_ADC_HB_SHIFT

| #define BQ2588X_TDIE_ADC_HB_SHIFT 0 |

◆ BQ2588X_TDIE_ADC_LB_BASE

| #define BQ2588X_TDIE_ADC_LB_BASE 0 |

◆ BQ2588X_TDIE_ADC_LB_LSB

| #define BQ2588X_TDIE_ADC_LB_LSB (1/2) |

◆ BQ2588X_TDIE_ADC_LB_MASK

| #define BQ2588X_TDIE_ADC_LB_MASK 0xFF |

◆ BQ2588X_TDIE_ADC_LB_SHIFT

| #define BQ2588X_TDIE_ADC_LB_SHIFT 0 |

◆ BQ2588X_TERM_DISABLE

| #define BQ2588X_TERM_DISABLE 0 |

◆ BQ2588X_TERM_EN_MASK

| #define BQ2588X_TERM_EN_MASK 0x80 |

◆ BQ2588X_TERM_EN_SHIFT

| #define BQ2588X_TERM_EN_SHIFT 7 |

◆ BQ2588X_TERM_ENABLE

| #define BQ2588X_TERM_ENABLE 1 |

◆ BQ2588X_TOPOFF_TIMER_15M

| #define BQ2588X_TOPOFF_TIMER_15M 1 |

◆ BQ2588X_TOPOFF_TIMER_30M

| #define BQ2588X_TOPOFF_TIMER_30M 2 |

◆ BQ2588X_TOPOFF_TIMER_45M

| #define BQ2588X_TOPOFF_TIMER_45M 3 |

◆ BQ2588X_TOPOFF_TIMER_DISABLE

| #define BQ2588X_TOPOFF_TIMER_DISABLE 0 |

◆ BQ2588X_TOPOFF_TIMER_MASK

| #define BQ2588X_TOPOFF_TIMER_MASK 0x30 |

◆ BQ2588X_TOPOFF_TIMER_SHIFT

| #define BQ2588X_TOPOFF_TIMER_SHIFT 4 |

◆ BQ2588X_TREG_FLAG_ACTIVE

| #define BQ2588X_TREG_FLAG_ACTIVE 1 |

◆ BQ2588X_TREG_FLAG_INACTIVE

| #define BQ2588X_TREG_FLAG_INACTIVE 0 |

◆ BQ2588X_TREG_FLAG_MASK

| #define BQ2588X_TREG_FLAG_MASK 0x10 |

◆ BQ2588X_TREG_FLAG_SHIFT

| #define BQ2588X_TREG_FLAG_SHIFT 4 |

◆ BQ2588X_TREG_INT_MASK_DISABLE

| #define BQ2588X_TREG_INT_MASK_DISABLE 0 |

◆ BQ2588X_TREG_INT_MASK_ENABLE

| #define BQ2588X_TREG_INT_MASK_ENABLE 1 |

◆ BQ2588X_TREG_INT_MASK_MASK

| #define BQ2588X_TREG_INT_MASK_MASK 0x10 |

◆ BQ2588X_TREG_INT_MASK_SHIFT

| #define BQ2588X_TREG_INT_MASK_SHIFT 4 |

◆ BQ2588X_TREG_STAT_ACTIVE

| #define BQ2588X_TREG_STAT_ACTIVE 1 |

◆ BQ2588X_TREG_STAT_INACTIVE

| #define BQ2588X_TREG_STAT_INACTIVE 0 |

◆ BQ2588X_TREG_STAT_MASK

| #define BQ2588X_TREG_STAT_MASK 0x10 |

◆ BQ2588X_TREG_STAT_SHIFT

| #define BQ2588X_TREG_STAT_SHIFT 4 |

◆ BQ2588X_TS_ADC_DIS_MASK

| #define BQ2588X_TS_ADC_DIS_MASK 0x04 |

◆ BQ2588X_TS_ADC_DIS_SHIFT

| #define BQ2588X_TS_ADC_DIS_SHIFT 2 |

◆ BQ2588X_TS_ADC_DISABLE

| #define BQ2588X_TS_ADC_DISABLE 1 |

◆ BQ2588X_TS_ADC_ENABLE

| #define BQ2588X_TS_ADC_ENABLE 0 |

◆ BQ2588X_TS_ADC_HB_BASE

| #define BQ2588X_TS_ADC_HB_BASE 0 |

◆ BQ2588X_TS_ADC_HB_LSB

| #define BQ2588X_TS_ADC_HB_LSB 25 |

◆ BQ2588X_TS_ADC_HB_MASK

| #define BQ2588X_TS_ADC_HB_MASK 0xFF |

◆ BQ2588X_TS_ADC_HB_SHIFT

| #define BQ2588X_TS_ADC_HB_SHIFT 0 |

◆ BQ2588X_TS_ADC_LB_BASE

| #define BQ2588X_TS_ADC_LB_BASE 0 |

◆ BQ2588X_TS_ADC_LB_LSB

| #define BQ2588X_TS_ADC_LB_LSB (25/256) |

◆ BQ2588X_TS_ADC_LB_MASK

| #define BQ2588X_TS_ADC_LB_MASK 0xFF |

◆ BQ2588X_TS_ADC_LB_SHIFT

| #define BQ2588X_TS_ADC_LB_SHIFT 0 |

◆ BQ2588X_TS_COLD

| #define BQ2588X_TS_COLD 3 |

◆ BQ2588X_TS_COOL

| #define BQ2588X_TS_COOL 2 |

◆ BQ2588X_TS_FLAG_CHANGED

| #define BQ2588X_TS_FLAG_CHANGED 1 |

◆ BQ2588X_TS_FLAG_MASK

| #define BQ2588X_TS_FLAG_MASK 0x04 |

◆ BQ2588X_TS_FLAG_NORMAL

| #define BQ2588X_TS_FLAG_NORMAL 0 |

◆ BQ2588X_TS_FLAG_SHIFT

| #define BQ2588X_TS_FLAG_SHIFT 2 |

◆ BQ2588X_TS_HOT

| #define BQ2588X_TS_HOT 4 |

◆ BQ2588X_TS_INT_MASK_DISABLE

| #define BQ2588X_TS_INT_MASK_DISABLE 0 |

◆ BQ2588X_TS_INT_MASK_ENABLE

| #define BQ2588X_TS_INT_MASK_ENABLE 1 |

◆ BQ2588X_TS_INT_MASK_MASK

| #define BQ2588X_TS_INT_MASK_MASK 0x04 |

◆ BQ2588X_TS_INT_MASK_SHIFT

| #define BQ2588X_TS_INT_MASK_SHIFT 2 |

◆ BQ2588X_TS_NORMAL

| #define BQ2588X_TS_NORMAL 0 |

◆ BQ2588X_TS_RSVED0

| #define BQ2588X_TS_RSVED0 5 |

◆ BQ2588X_TS_RSVED1

| #define BQ2588X_TS_RSVED1 6 |

◆ BQ2588X_TS_RSVED2

| #define BQ2588X_TS_RSVED2 7 |

◆ BQ2588X_TS_STAT_MASK

| #define BQ2588X_TS_STAT_MASK 0x07 |

◆ BQ2588X_TS_STAT_SHIFT

| #define BQ2588X_TS_STAT_SHIFT 0 |

◆ BQ2588X_TS_WARM

| #define BQ2588X_TS_WARM 1 |

◆ BQ2588X_TSHUT_FLAG_ACTIVE

| #define BQ2588X_TSHUT_FLAG_ACTIVE 1 |

◆ BQ2588X_TSHUT_FLAG_INACTIVE

| #define BQ2588X_TSHUT_FLAG_INACTIVE 0 |

◆ BQ2588X_TSHUT_FLAG_MASK

| #define BQ2588X_TSHUT_FLAG_MASK 0x40 |

◆ BQ2588X_TSHUT_FLAG_SHIFT

| #define BQ2588X_TSHUT_FLAG_SHIFT 6 |

◆ BQ2588X_TSHUT_INT_MASK_DISABLE

| #define BQ2588X_TSHUT_INT_MASK_DISABLE 0 |

◆ BQ2588X_TSHUT_INT_MASK_ENABLE

| #define BQ2588X_TSHUT_INT_MASK_ENABLE 1 |

◆ BQ2588X_TSHUT_INT_MASK_MASK

| #define BQ2588X_TSHUT_INT_MASK_MASK 0x40 |

◆ BQ2588X_TSHUT_INT_MASK_SHIFT

| #define BQ2588X_TSHUT_INT_MASK_SHIFT 6 |

◆ BQ2588X_TSHUT_STAT_ACTIVE

| #define BQ2588X_TSHUT_STAT_ACTIVE 1 |

◆ BQ2588X_TSHUT_STAT_INACTIVE

| #define BQ2588X_TSHUT_STAT_INACTIVE 0 |

◆ BQ2588X_TSHUT_STAT_MASK

| #define BQ2588X_TSHUT_STAT_MASK 0x40 |

◆ BQ2588X_TSHUT_STAT_SHIFT

| #define BQ2588X_TSHUT_STAT_SHIFT 6 |

◆ BQ2588X_VBAT_ADC_DIS_MASK

| #define BQ2588X_VBAT_ADC_DIS_MASK 0x10 |

◆ BQ2588X_VBAT_ADC_DIS_SHIFT

| #define BQ2588X_VBAT_ADC_DIS_SHIFT 4 |

◆ BQ2588X_VBAT_ADC_DISABLE

| #define BQ2588X_VBAT_ADC_DISABLE 1 |

◆ BQ2588X_VBAT_ADC_ENABLE

| #define BQ2588X_VBAT_ADC_ENABLE 0 |

◆ BQ2588X_VBAT_ADC_HB_BASE

| #define BQ2588X_VBAT_ADC_HB_BASE 0 |

◆ BQ2588X_VBAT_ADC_HB_LSB

| #define BQ2588X_VBAT_ADC_HB_LSB 256 |

◆ BQ2588X_VBAT_ADC_HB_MASK

| #define BQ2588X_VBAT_ADC_HB_MASK 0xFF |

◆ BQ2588X_VBAT_ADC_HB_SHIFT

| #define BQ2588X_VBAT_ADC_HB_SHIFT 0 |

◆ BQ2588X_VBAT_ADC_LB_BASE

| #define BQ2588X_VBAT_ADC_LB_BASE 0 |

◆ BQ2588X_VBAT_ADC_LB_LSB

| #define BQ2588X_VBAT_ADC_LB_LSB 1 |

◆ BQ2588X_VBAT_ADC_LB_MASK

| #define BQ2588X_VBAT_ADC_LB_MASK 0xFF |

◆ BQ2588X_VBAT_ADC_LB_SHIFT

| #define BQ2588X_VBAT_ADC_LB_SHIFT 0 |

◆ BQ2588X_VBUS_ADC_DIS_MASK

| #define BQ2588X_VBUS_ADC_DIS_MASK 0x20 |

◆ BQ2588X_VBUS_ADC_DIS_SHIFT

| #define BQ2588X_VBUS_ADC_DIS_SHIFT 5 |

◆ BQ2588X_VBUS_ADC_DISABLE

| #define BQ2588X_VBUS_ADC_DISABLE 1 |

◆ BQ2588X_VBUS_ADC_ENABLE

| #define BQ2588X_VBUS_ADC_ENABLE 0 |

◆ BQ2588X_VBUS_ADC_HB_BASE

| #define BQ2588X_VBUS_ADC_HB_BASE 0 |

◆ BQ2588X_VBUS_ADC_HB_LSB

| #define BQ2588X_VBUS_ADC_HB_LSB 256 |

◆ BQ2588X_VBUS_ADC_HB_MASK

| #define BQ2588X_VBUS_ADC_HB_MASK 0xFF |

◆ BQ2588X_VBUS_ADC_HB_SHIFT

| #define BQ2588X_VBUS_ADC_HB_SHIFT 0 |

◆ BQ2588X_VBUS_ADC_LB_BASE

| #define BQ2588X_VBUS_ADC_LB_BASE 0 |

◆ BQ2588X_VBUS_ADC_LB_LSB

| #define BQ2588X_VBUS_ADC_LB_LSB 1 |

◆ BQ2588X_VBUS_ADC_LB_MASK

| #define BQ2588X_VBUS_ADC_LB_MASK 0xFF |

◆ BQ2588X_VBUS_ADC_LB_SHIFT

| #define BQ2588X_VBUS_ADC_LB_SHIFT 0 |

◆ BQ2588X_VBUS_FLAG_CHANGED

| #define BQ2588X_VBUS_FLAG_CHANGED 1 |

◆ BQ2588X_VBUS_FLAG_MASK

| #define BQ2588X_VBUS_FLAG_MASK 0x10 |

◆ BQ2588X_VBUS_FLAG_NORMAL

| #define BQ2588X_VBUS_FLAG_NORMAL 0 |

◆ BQ2588X_VBUS_FLAG_SHIFT

| #define BQ2588X_VBUS_FLAG_SHIFT 4 |

◆ BQ2588X_VBUS_INT_MASK_DISABLE

| #define BQ2588X_VBUS_INT_MASK_DISABLE 0 |

◆ BQ2588X_VBUS_INT_MASK_ENABLE

| #define BQ2588X_VBUS_INT_MASK_ENABLE 1 |

◆ BQ2588X_VBUS_INT_MASK_MASK

| #define BQ2588X_VBUS_INT_MASK_MASK 0x10 |

◆ BQ2588X_VBUS_INT_MASK_SHIFT

| #define BQ2588X_VBUS_INT_MASK_SHIFT 4 |

◆ BQ2588X_VBUS_NO_INPUT

| #define BQ2588X_VBUS_NO_INPUT 0 |

◆ BQ2588X_VBUS_OTG_MODE

| #define BQ2588X_VBUS_OTG_MODE 7 |

◆ BQ2588X_VBUS_OVP_FLAG_ACTIVE

| #define BQ2588X_VBUS_OVP_FLAG_ACTIVE 1 |

◆ BQ2588X_VBUS_OVP_FLAG_INACTIVE

| #define BQ2588X_VBUS_OVP_FLAG_INACTIVE 0 |

◆ BQ2588X_VBUS_OVP_FLAG_MASK

| #define BQ2588X_VBUS_OVP_FLAG_MASK 0x80 |

◆ BQ2588X_VBUS_OVP_FLAG_SHIFT

| #define BQ2588X_VBUS_OVP_FLAG_SHIFT 7 |

◆ BQ2588X_VBUS_OVP_INT_MASK_DISABLE

| #define BQ2588X_VBUS_OVP_INT_MASK_DISABLE 0 |

◆ BQ2588X_VBUS_OVP_INT_MASK_ENABLE

| #define BQ2588X_VBUS_OVP_INT_MASK_ENABLE 1 |

◆ BQ2588X_VBUS_OVP_INT_MASK_MASK

| #define BQ2588X_VBUS_OVP_INT_MASK_MASK 0x80 |

◆ BQ2588X_VBUS_OVP_INT_MASK_SHIFT

| #define BQ2588X_VBUS_OVP_INT_MASK_SHIFT 7 |

◆ BQ2588X_VBUS_OVP_STAT_ACTIVE

| #define BQ2588X_VBUS_OVP_STAT_ACTIVE 1 |

◆ BQ2588X_VBUS_OVP_STAT_INACTIVE

| #define BQ2588X_VBUS_OVP_STAT_INACTIVE 0 |

◆ BQ2588X_VBUS_OVP_STAT_MASK

| #define BQ2588X_VBUS_OVP_STAT_MASK 0x80 |

◆ BQ2588X_VBUS_OVP_STAT_SHIFT

| #define BQ2588X_VBUS_OVP_STAT_SHIFT 7 |

◆ BQ2588X_VBUS_POOR_SRC

| #define BQ2588X_VBUS_POOR_SRC 4 |

◆ BQ2588X_VBUS_STAT_MASK

| #define BQ2588X_VBUS_STAT_MASK 0x70 |

◆ BQ2588X_VBUS_STAT_SHIFT

| #define BQ2588X_VBUS_STAT_SHIFT 4 |

◆ BQ2588X_VBUS_USB_CDP

| #define BQ2588X_VBUS_USB_CDP 2 |

◆ BQ2588X_VBUS_USB_DCP

| #define BQ2588X_VBUS_USB_DCP 3 |

◆ BQ2588X_VBUS_USB_NON_STANDARD

| #define BQ2588X_VBUS_USB_NON_STANDARD 6 |

◆ BQ2588X_VBUS_USB_SDP

| #define BQ2588X_VBUS_USB_SDP 1 |

◆ BQ2588X_VBUS_USB_UNKNOWN

| #define BQ2588X_VBUS_USB_UNKNOWN 5 |

◆ BQ2588X_VINDPM_FLAG_ACTIVE

| #define BQ2588X_VINDPM_FLAG_ACTIVE 1 |

◆ BQ2588X_VINDPM_FLAG_INACTIVE

| #define BQ2588X_VINDPM_FLAG_INACTIVE 0 |

◆ BQ2588X_VINDPM_FLAG_MASK

| #define BQ2588X_VINDPM_FLAG_MASK 0x20 |

◆ BQ2588X_VINDPM_FLAG_SHIFT

| #define BQ2588X_VINDPM_FLAG_SHIFT 5 |

◆ BQ2588X_VINDPM_INT_MASK_DISABLE

| #define BQ2588X_VINDPM_INT_MASK_DISABLE 0 |

◆ BQ2588X_VINDPM_INT_MASK_ENABLE

| #define BQ2588X_VINDPM_INT_MASK_ENABLE 1 |

◆ BQ2588X_VINDPM_INT_MASK_MASK

| #define BQ2588X_VINDPM_INT_MASK_MASK 0x20 |

◆ BQ2588X_VINDPM_INT_MASK_SHIFT

| #define BQ2588X_VINDPM_INT_MASK_SHIFT 5 |

◆ BQ2588X_VINDPM_RESET_DISABLE

| #define BQ2588X_VINDPM_RESET_DISABLE 0 |

◆ BQ2588X_VINDPM_RESET_EN_MASK

| #define BQ2588X_VINDPM_RESET_EN_MASK 0x80 |

◆ BQ2588X_VINDPM_RESET_EN_SHIFT

| #define BQ2588X_VINDPM_RESET_EN_SHIFT 7 |

◆ BQ2588X_VINDPM_RESET_ENABLE

| #define BQ2588X_VINDPM_RESET_ENABLE 1 |

◆ BQ2588X_VINDPM_STAT_ACTIVE

| #define BQ2588X_VINDPM_STAT_ACTIVE 1 |

◆ BQ2588X_VINDPM_STAT_INACTIVE

| #define BQ2588X_VINDPM_STAT_INACTIVE 0 |

◆ BQ2588X_VINDPM_STAT_MASK

| #define BQ2588X_VINDPM_STAT_MASK 0x20 |

◆ BQ2588X_VINDPM_STAT_SHIFT

| #define BQ2588X_VINDPM_STAT_SHIFT 5 |

◆ BQ2588X_VINDPM_TH_BASE

| #define BQ2588X_VINDPM_TH_BASE 3900 |

◆ BQ2588X_VINDPM_TH_LSB

| #define BQ2588X_VINDPM_TH_LSB 100 |

◆ BQ2588X_VINDPM_TH_MASK

| #define BQ2588X_VINDPM_TH_MASK 0x1F |

◆ BQ2588X_VINDPM_TH_SHIFT

| #define BQ2588X_VINDPM_TH_SHIFT 0 |

◆ BQ2588X_VREG_BASE

| #define BQ2588X_VREG_BASE 6800 |

◆ BQ2588X_VREG_LSB

| #define BQ2588X_VREG_LSB 10 |

◆ BQ2588X_VREG_MASK

| #define BQ2588X_VREG_MASK 0xFF |

◆ BQ2588X_VREG_SHIFT

| #define BQ2588X_VREG_SHIFT 0 |

◆ BQ2588X_VSYS_ADC_DIS_MASK

| #define BQ2588X_VSYS_ADC_DIS_MASK 0x08 |

◆ BQ2588X_VSYS_ADC_DIS_SHIFT

| #define BQ2588X_VSYS_ADC_DIS_SHIFT 3 |

◆ BQ2588X_VSYS_ADC_DISABLE

| #define BQ2588X_VSYS_ADC_DISABLE 1 |

◆ BQ2588X_VSYS_ADC_ENABLE

| #define BQ2588X_VSYS_ADC_ENABLE 0 |

◆ BQ2588X_VSYS_ADC_HB_BASE

| #define BQ2588X_VSYS_ADC_HB_BASE 0 |

◆ BQ2588X_VSYS_ADC_HB_LSB

| #define BQ2588X_VSYS_ADC_HB_LSB 256 |

◆ BQ2588X_VSYS_ADC_HB_MASK

| #define BQ2588X_VSYS_ADC_HB_MASK 0xFF |

◆ BQ2588X_VSYS_ADC_HB_SHIFT

| #define BQ2588X_VSYS_ADC_HB_SHIFT 0 |

◆ BQ2588X_VSYS_ADC_LB_BASE

| #define BQ2588X_VSYS_ADC_LB_BASE 0 |

◆ BQ2588X_VSYS_ADC_LB_LSB

| #define BQ2588X_VSYS_ADC_LB_LSB 1 |

◆ BQ2588X_VSYS_ADC_LB_MASK

| #define BQ2588X_VSYS_ADC_LB_MASK 0xFF |

◆ BQ2588X_VSYS_ADC_LB_SHIFT

| #define BQ2588X_VSYS_ADC_LB_SHIFT 0 |

◆ BQ2588X_VSYS_FLAG_CHANGED

| #define BQ2588X_VSYS_FLAG_CHANGED 1 |

◆ BQ2588X_VSYS_FLAG_MASK

| #define BQ2588X_VSYS_FLAG_MASK 0x01 |

◆ BQ2588X_VSYS_FLAG_NORMAL

| #define BQ2588X_VSYS_FLAG_NORMAL 0 |

◆ BQ2588X_VSYS_FLAG_SHIFT

| #define BQ2588X_VSYS_FLAG_SHIFT 0 |

◆ BQ2588X_VSYS_INT_MASK_DISABLE

| #define BQ2588X_VSYS_INT_MASK_DISABLE 0 |

◆ BQ2588X_VSYS_INT_MASK_ENABLE

| #define BQ2588X_VSYS_INT_MASK_ENABLE 1 |

◆ BQ2588X_VSYS_INT_MASK_MASK

| #define BQ2588X_VSYS_INT_MASK_MASK 0x01 |

◆ BQ2588X_VSYS_INT_MASK_SHIFT

| #define BQ2588X_VSYS_INT_MASK_SHIFT 0 |

◆ BQ2588X_WDT_FLAG_EXPIRED

| #define BQ2588X_WDT_FLAG_EXPIRED 1 |

◆ BQ2588X_WDT_FLAG_MASK

| #define BQ2588X_WDT_FLAG_MASK 0x08 |

◆ BQ2588X_WDT_FLAG_NORMAL

| #define BQ2588X_WDT_FLAG_NORMAL 0 |

◆ BQ2588X_WDT_FLAG_SHIFT

| #define BQ2588X_WDT_FLAG_SHIFT 3 |

◆ BQ2588X_WDT_INT_MASK_DISABLE

| #define BQ2588X_WDT_INT_MASK_DISABLE 0 |

◆ BQ2588X_WDT_INT_MASK_ENABLE

| #define BQ2588X_WDT_INT_MASK_ENABLE 1 |

◆ BQ2588X_WDT_INT_MASK_MASK

| #define BQ2588X_WDT_INT_MASK_MASK 0x08 |

◆ BQ2588X_WDT_INT_MASK_SHIFT

| #define BQ2588X_WDT_INT_MASK_SHIFT 3 |

◆ BQ2588X_WDT_RESET

| #define BQ2588X_WDT_RESET 1 |

◆ BQ2588X_WDT_RESET_DISABLE

| #define BQ2588X_WDT_RESET_DISABLE 0 |

◆ BQ2588X_WDT_RESET_MASK

| #define BQ2588X_WDT_RESET_MASK 0x40 |

◆ BQ2588X_WDT_RESET_SHIFT

| #define BQ2588X_WDT_RESET_SHIFT 6 |

◆ BQ2588X_WDT_STAT_EXPIRED

| #define BQ2588X_WDT_STAT_EXPIRED 1 |

◆ BQ2588X_WDT_STAT_INACTIVE

| #define BQ2588X_WDT_STAT_INACTIVE 0 |

◆ BQ2588X_WDT_STAT_MASK

| #define BQ2588X_WDT_STAT_MASK 0x08 |

◆ BQ2588X_WDT_STAT_SHIFT

| #define BQ2588X_WDT_STAT_SHIFT 3 |

◆ BQ2588X_WDT_TIMER_160S

| #define BQ2588X_WDT_TIMER_160S 3 |

◆ BQ2588X_WDT_TIMER_40S

| #define BQ2588X_WDT_TIMER_40S 1 |

◆ BQ2588X_WDT_TIMER_80S

| #define BQ2588X_WDT_TIMER_80S 2 |

◆ BQ2588X_WDT_TIMER_DISABLE

| #define BQ2588X_WDT_TIMER_DISABLE 0 |

◆ BQ2588X_WDT_TIMER_MASK

| #define BQ2588X_WDT_TIMER_MASK 0x30 |

◆ BQ2588X_WDT_TIMER_SHIFT

| #define BQ2588X_WDT_TIMER_SHIFT 4 |